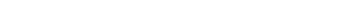

Design quality is manufactured quality. We provide schematic and PCB layout support with the added perspective of an experienced manufacturer — so layout decisions also support assembly, inspection, and scaling to production.

A PCB can be electrically correct and still be difficult to build, test, or scale. Circuits Central brings manufacturing perspective into the design process — so the decisions made during layout also support assembly, inspection, and future production.

Manufacturing-aligned design: Because we also build and test PCBs, we understand what good documentation looks like from the assembler’s perspective. That experience reduces re-spins, prevents avoidable rework, and shortens the gap between first prototype and production-ready design.

Requirements & Block Diagrams

System-level definition, interface mapping, and block diagram development to establish design intent before schematic capture begins.

Schematic Capture

Structured schematic development with review for electrical correctness, net clarity, revision control, and design intent documentation.

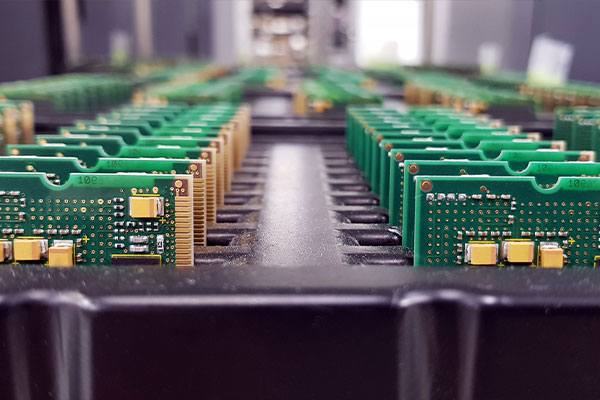

Footprint & Library Development

Land patterns, pin-1 marking, polarity indicators, and courtyard definitions that are consistent from schematic to the assembly drawing.

Placement, Routing & Constraints

Layout with performance, EMI risk reduction, and manufacturability in mind — constraint-driven from day one, not corrected in DRC at the end.

DFM & DFT Integration

Test point placement, boundary-scan planning, connector strategy, and assembly access reviews built into the design workflow.

Production-Ready Deliverables

Gerbers or ODB++, drill files, pick-and-place, assembly drawings, BOM with alternates, and bring-up notes — a complete handoff package.

Why this matters at the design stage: A footprint error or single-source component costs relatively little to fix in schematic. The same issue costs significantly more to resolve after boards are fabricated, components are committed, and the first prototype comes back with a bring-up problem that traces back to a library entry.

Component decisions made during schematic capture have consequences that persist through every build revision. A part selected without checking lifecycle status, package availability, or footprint tolerance can create sourcing bottlenecks, assembly friction, or redesign work that shows up months later — often at the worst moment in a product schedule. We address this upstream, during the design phase, not at the BOM review stage before a build.

In practice this means:

Test coverage during bring-up and in production is largely determined by decisions made during PCB layout — not by the test engineer after the board is built. Test points that weren’t placed, boundary-scan chains that weren’t planned, and programming connectors that weren’t sized for a pogo pin fixture are difficult or impossible to retrofit cleanly. We include DFT as a defined part of the layout process, not an afterthought.

DFT considerations we address during layout include:

For teams that already have an ICT fixture, a functional test script, or a defined bring-up procedure, we review those requirements before layout begins so that test access is planned to match — not approximated and corrected after the fact.

| Engagement | Best Suited For | Considerations |

|---|---|---|

| DFM Review & Feedback | Designs near release — targeted improvements before fabrication | Best when design is largely complete; cannot replace missing requirements |

| Layout Only | Complete schematic provided — focused on placement, routing, and outputs | Requires complete schematic and library clarity before starting |

| Full Design | Requirements to production-ready layout under one team | Up-front discovery phase is essential; missing requirements cause late changes |

| Design + Prototype Build | Short feedback loop between design intent and build results | Requires coordinated schedule for sourcing, assembly, and bring-up support |

Trustindex verifies that the original source of the review is Google. Excellent PCB assembly services. We have had an excellent experience with Circuits Central. - Turn Around Time: Boards were always assembled on time including expedited projects with 24-hour TAT. - Customer Service: Customer service is fast to respond over email and resolve any outstanding issues very quickly. - Quality: Excellent assembly quality with no errors or issues including for complex projects. - Communication: Circuits Central made the jobs simple to submit. We didn't have to submit many files or prepare every last detail for them.Posted onTrustindex verifies that the original source of the review is Google. Circuits Central has been making our boards for over 25 years. They are a great company to work with.Posted onTrustindex verifies that the original source of the review is Google. Great customer service! Highly recommend the team at CCIPosted onTrustindex verifies that the original source of the review is Google. I've been using Circuits Central for over 10 years for all of our NPI projects. Workmanship is exceptional and deliveries are always on time. Many thanks to the Circuits Central team.Posted onTrustindex verifies that the original source of the review is Google. Excellent service and printed circuit assembly quality for 6 years so far, at a very reasonable price. Highly recommended!Posted onTrustindex verifies that the original source of the review is Google. Tailored Service Levels and Pricing. Excellent quality!

Please fill out the form below and we will get in touch with you to further discuss your needs.